Synopsys Design Vision

From CVL Wiki

What is Synopsys Design Vision

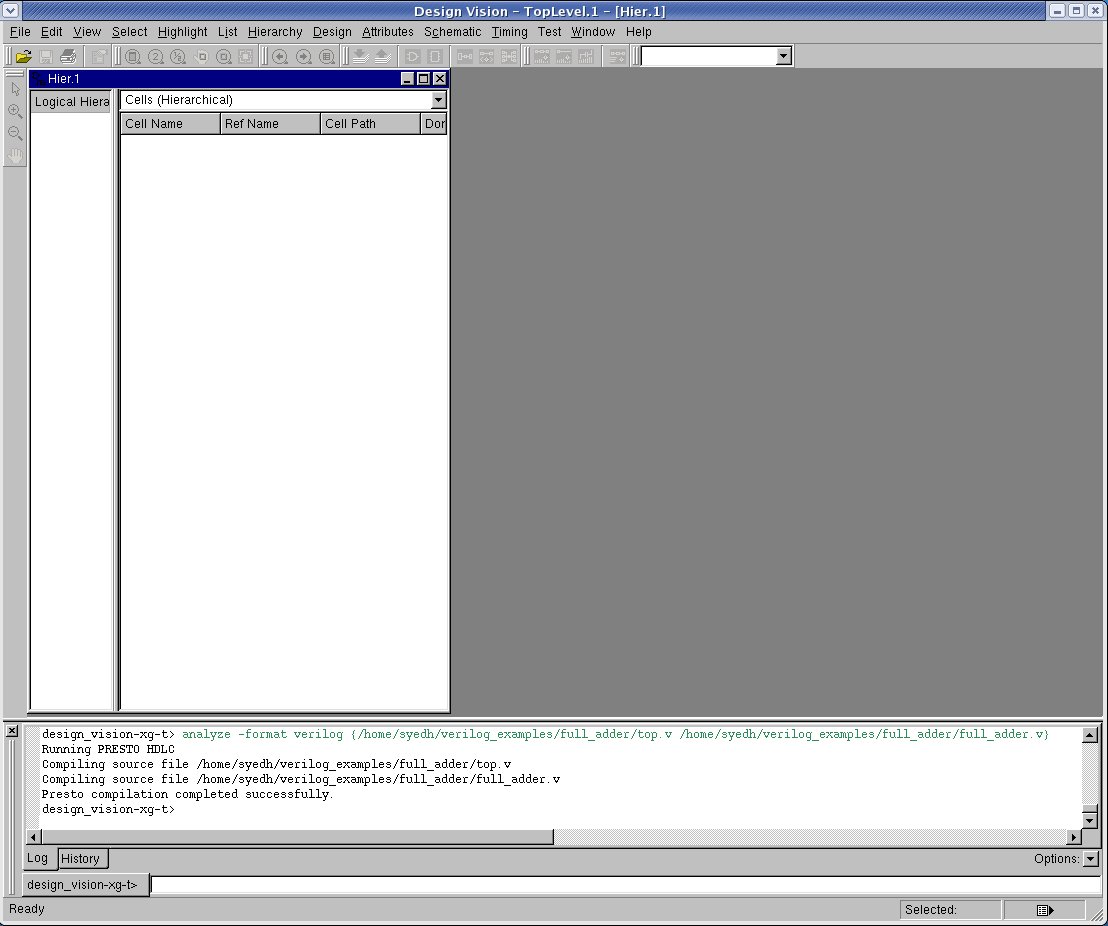

Synopsys Design Vision is a logic synthesis tool. It will take HDL designs and synthesize them to gate-level HDL netlists. Both verilog and vhdl languages are supported. It can synthesize to generic gates or to other design libraries such as the vtvt_tsmc libraries or OSU standard cell libraries. The tool exists in a gui and command line version. The gui version is referred to as design vision and the command line version is known as dc_shell-xg-t.

How to start Synopsys Design Vision

In the cvl or cesca cluster type the following commands to start the gui version:

Synopsys design_vision

To start the command shell of the tool instead type:

Synopsys dc_shell-xg-t

Basic Steps to Synthesizing Design

The basic steps:

- Analyze

This step checks the design files for syntax. This step also saves modules (verilog) and entities (vhdl) into a local folder in a intermediate format.

- Elaborate

This step builds a design from the intermediate format files created in the Elaborate step.

- Compile

This is the synthesizing step. Here the design is mapped to a gate library or cell library.

- Save

After compiling a design one can save the synthesized design into HDL or other formats. Synthesized designs are integral toward creating ASICS or performing different simulations for timing and power.

A sample tutorial for Power estimation goes through these steps: Synopsys Tutorial: Power Estimation